NIOS II中PIO有关寄存器

寄存器映射

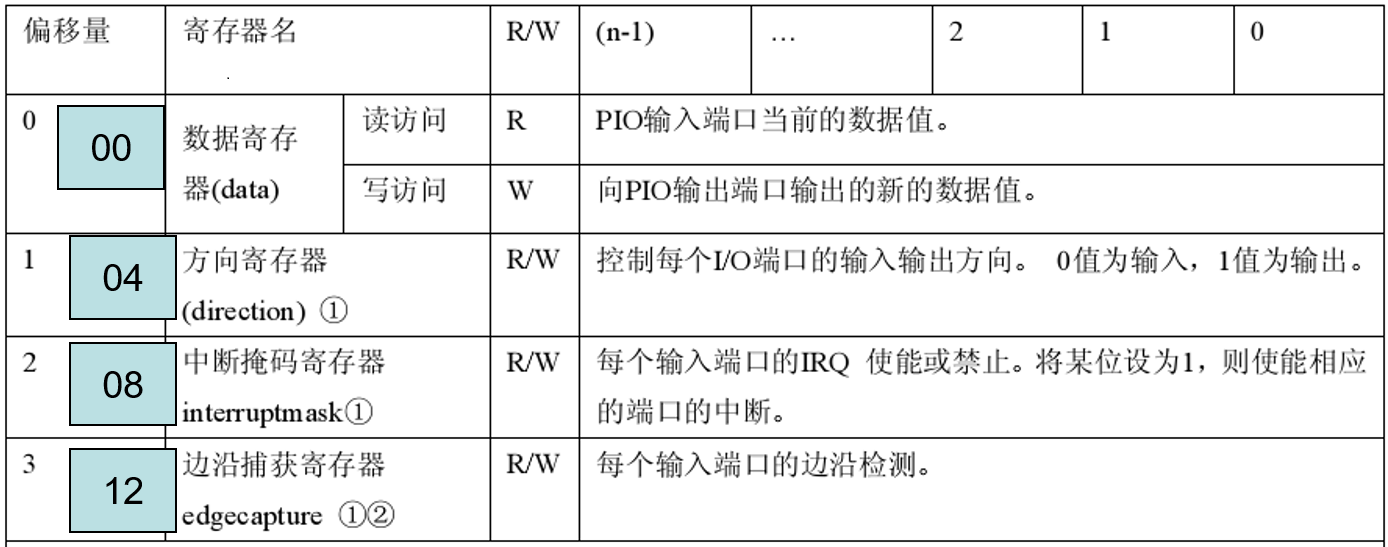

Avalon-MM主外设,例如CPU,通过4个32位寄存器控制并与PIO核通信,假定PIO核的I/O端口被配置为n位宽度。如下图:

(1) 该寄存器是否存在取决于硬件配置,如果寄存器不存在,读寄存器返回一个未定义的值,写寄存器无影响。

(2) 写任何值到edgecapture,会清0所有位。

数据寄存器

读从Data寄存器返回的呈现在输入端口的值。如果PIO核硬件被配置为output-only(只输出)模式,读data寄存器将返回一个未定义的值。

写data寄存器将存储值到寄存器中以驱动输出端口。如果PIO核硬件被配置为input-only(只输入)模式,写data寄存器无影响。如果PIO核硬件被配置为双向模式,则仅当在 direction(方向)寄存器中相应的位被置1(输出)时,被寄存的值才会出现在输出端口上。

方向寄存器

direction(方向)寄存器控制每个PIO端口的数据方向,假定端口是双向的,当位n在方向寄存器中被置1时,端口n在data(数据)寄存器的相应位驱动输出值。

仅当PIO核硬件被配置为双向模式时,direction寄存器才存在。模式(输入、输出或双向)在系统创建时指定,并且在运行时不能修改。在输入或输出模式中,direction寄存器不存在,在这种情况下,读direction返回一个未定义的值,写direction无影响。

在复位后,方向寄存器的所有位都是0,所以所有双向I/O端口都被配置为输入。如果那些PIO端口被连接到FPGA器件的引脚,则这些引脚保持高阻状态。在双向模式,为了改变PIO端口的方向,要重新编程direction寄存器。

中断屏蔽寄存器

设置interruptmask Register(中断屏蔽寄存器)中的位为1允许相应PIO输入端口中断。中断行为取决于PIO核的硬件配置。见“中断行为”。

interruptmask寄存器仅当硬件被配置为能产生IRQ时才存在。如果PIO核不能产生IRQ,读interruptmask返回一个未定义的值,写interruptmask无影响。

在复位后,所有interruptmask寄存器的位都是0,所以所有的PIO端口中断都被禁用。

边沿捕获寄存器

如果edgecapture(边沿捕获)寄存器中的位n被设置位1,在输入端口n上的边沿将会被探测到。Avalon-MM主外设能够读edgecapture寄存器以确定是否有一个边沿出现在任何PIO输入端口。写任何值到edgecapture将清除寄存器中的所有位。

要探测的边沿的类型在系统创建时就已经选定在硬件中。edgecapture寄存器只能在硬件被配置位捕获边沿时存在。如果PIO核没有被配置成捕获边沿,读edgecapture将返回一个未定义的值,写edgecapture无影响。

输出置位和输出清零寄存器

你可以使用输出置位和输出清零(outset和outclear)寄存器置1或清0指定的输出端口的位。例如,要设置输出端口的第六位,可以写0x40(0100 0000)到outset寄存器。写0x08(0000 1000)到outclear寄存器可清0输出端口的第3位。

这些寄存器只有在选择Enable individual bit set/clear output register寄存器为开启时才可用。

中断行为

PIO核输出一个能够连接到任意在系统中的主外设的单个IRQ信号。主外设既能够读dagta寄存器,也能够edgecapture寄存器以确定那一个输入端口引发了中断。

当硬件被配置为电平敏感中断时,当data和interruptmask寄存器中相应的位是1时,IRQ被确定。当硬件被配置为边沿敏感中断时,当edgecapture和interruptmask寄存器中相应的位是1时,IRQ被确定。IRQ保持确定直到禁用interruptmask中相应的位或者写edgecapture相应的位以明确地确认为止。

参考:

Chentuo’s《PIO Core》